# PDP-10/X System Manual

Dave Conroy (dgc@fpgaretrocomputing.org)

April 24, 2012

| 12-Jan-2008 | Initial version. Based on the text from the LaTeX version, but considerably reworked to include all of the thinking about how the APR device should work, how traps and errors should work, and so on. None of the hardware that has been designed so far conforms to this specification, although its not wrong by much.                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30-Jan-2008 | I finally figured out the right way for the address mapping while the ROM is running to work (and I got to use the word moby in one of the canonical ways). Major changes to the section on PAG, and the section that describes how the ROM works.                                                                                                                                                                      |

| 02-Apr-2008 | Minor revisions, mainly around the implementation of floating point, including KA-style double precision. Some reformatting of the opcode table to make it more readable.                                                                                                                                                                                                                                               |

| 21-May-2008 | Changed the way the APR interrupts for bus and paging errors get generated. In the old design there were flags for bus error and paging error. In the new design there are flags for soft error and hard error, and a soft error is sometimes turned into a hard error. This works better because a soft error generated in a PI routine will get transformed into a hard error (and get into DDT) rather than halting. |

| 01-Jun-2008 | Changed the RTC device to include the 36-bit free-running timer.                                                                                                                                                                                                                                                                                                                                                        |

| 08-Jun-2008 | Changed the RTC device to so that the 36-bit free-running timer is reset by the power-on reset, not the $I/O$ reset. This allows the ROM to read the date/time clock once, rather than having to teach ITS how to read it after every $I/O$ reset.                                                                                                                                                                      |

| 23-Jun-2008 | Changed the way APR interrupts work again, this time to make it easy to context switch the trap enables and (possibly) ask for a fake soft error (needed by code that uses XCTRI) with a single CONO.                                                                                                                                                                                                                   |

| 14-Jul-2008 | Changed all of the ASCII art for instructions and registers to use tables in a clever way. There are still some ugly page breaks, but overall the idea of using tables with no edge lines in some cases works.                                                                                                                                                                                                          |

| 17-Jul-2008 | Eliminated previous mode. XCTR and XCTRI always redirect into user mode. This is what ITS really wanted. Removed a bunch of JRSTF instructions from ITS whose only purpose was to force $PM=1$ .                                                                                                                                                                                                                        |

| 27-Sep-2009 | Switched to the DS1337 real-time clock. The DS1337 does not have the DS1338s 56 bytes of non-volatile memory, but does come in a wider array of packaging options, including an 8-bit DIP option that is well suited to being used on a prototype.                                                                                                                                                                      |

| 20-Mar-2011 | Added a new section to describe the ETH interface, including details of how the 16-bit and 32-bit packing and unpacking works.                                                                                                                                                                                                                                                                                          |

| 18-Feb-2012 | Switching from LaTeX was a mistake, so I switched back. Added the TA bit to the TTY device so that the transmit side could be flushed before an I/O reset. Added a new section to APR that describes how software can determine that this is indeed a new implementation of the architecture.                                                                                                                           |

# Introduction

This document describes the PDP-10/X, a new implementation of the venerable PDP-10 architecture from Digital Equipment Corporation.

This document describes the PDP-10/X at a level appropriate for assembly language programmers, and includes considerable information regarding low-level I/O device programming. It is not a complete description of the PDP-10 architecture (the original DEC manuals serve this function), although does describe details of the architecture in places where the DEC manuals are unclear and/or there is a tradition of variation from model to model. It is also not a complete description of some of the I/O components (the manufacturer's data sheets and external standards serve this function), although it does describe how the components are interconnected.

The PDP-10/X has three major blocks.

The first block is the processor (APR). The APR block is a new hardwired model of the PDP-10 that most closely resembles a KA10 to which ITS paging has been added (for example, it implements KA10-style floating point arithmetic, it has one block of ACs, the MUUO and PI instructions are read from fixed locations in memory, and APR conditions such as traps and page failures are reported using the PI system) but which is not exactly compatible with the KA10 (for example, some of the quirks of the KA10s implementation that were fixed in all later models are fixed).

The second block is the pager and memory controller (PAG). The PAG block responds to all memory references made by the APR block, translating virtual memory addresses into physical memory addresses, in a way that is appropriate for ITS, when necessary. The PAG block implements 22-bit addressing, but the PDP-10/X only implements 512KW of memory (using five 512Kx8 55ns SRAMs) so only 19 address bits are actually used. It might seem more appropriate to perform address translation in the APR block, but putting it in the PAG block allows the in-memory structures used when translating addresses to be accessed more efficiently.

The third block is the basic I/O system (BIO). The BIO block contains the I/O devices needed by a basic, but complete, ITS system; a line frequency clock, an real-time clock with a battery backup (to keep track of the date and time, even when the system is not running), a console terminal interfaces, a disk interface, and an ethernet interface.

The line frequency clock does not actually run off the line (it runs off the crystal used to generate the bit clock for the console terminal) so it always runs at 60 Hz, even if the system is running off a battery.

The console terminal interface communicates with 2-wire RS-232 devices at 9600 bits per second. The programming model is more like a traditional DEC interface than any industry-standard interface, and is designed to simplify the modifications to the ITS terminal driver (a previous PDP-10 design used an industry-standard 16450/16550 UART, and the modifications to the ITS terminal driver to handle such a UART were harder to do than they first appeared to be; its hard to make a 16450/16550 generate a transmit-side PI on demand).

The disk interface drives one or two ATA-2 disks. All disk transfers are performed using programmed I/O (programmed I/O is almost as good as DMA in a system like the PDP-10/X, since an ATA-2 disk contains a sector buffer, and provides data in a long burst that would monopolize the memory and cause the APR to stop dead anyway), and since disk DMA is not used, disk-like devices that are more-or-less compatible with the ATA-2 standard but do not support DMA (like compact flash cards) can be used. The disk interface does not resemble any traditional PDP-10 design.

The ethernet interface drives a WizNet WIZ830MJ embedded ethernet module, which uses the WizNet W5300 ethernet controller. The controller can be run either in a mode where it is little more than an ethernet chip with 128KB of shared buffering or in a mode where it contains a complete, albeit fairly simple, TCP/UDP/ICMP/IP stack (which is useful when writing simple stand-alone applications that need to talk to the network). The ethernet interface can transfer data between the APR and the W5300 in either big-endian or little-endian order, both of which are used by the CHAOSNET.

The three blocks (APR, PAG, BIO) are fairly independent, and at one point in time the PDP-10/X plan was to place them in three separate FPGAs, and generate clocks and resets using MSI components. However, all three blocks ended up fitting (with quite a lot of space to spare) in a single FPGA, and this is how the PDP-10/X is actually constructed.

The PDP-10/X runs a custom version of the Incompatible Timesharing System (ITS), created and maintained at MIT between 1966 and 1990. The PDP-10/X runs ITS both for its obvious hack value, and because a complex project like the PDP-10/X is best tackled in stages, and ITS will run on a somewhat simpler system than either TOPS-10 or TOPS-20/TENEX. Some thought has been given to running TOPS-10 and/or TOPS-20/TENEX, and the structure of the system is suitable for building a version of the PDP-10/X capable of running a modified version of TOPS-10 and/or TOPS-20/TENEX (the vast majority of the changes to the hardware are, of course, in the PAG block).

## APR

#### 2.1 Instruction Formats

The APR implements the user-mode architecture of the KA10 (including the somewhat odd KA10 double-precision floating point), although it does not replicate the quirks of the KA10 that were eliminated from all later models (for example, the fact that adjustments to things like stack and byte pointers were done with fullword adds and subtracts, and that a carry in the right half could ripple into the left half), nor does it replicate the incorrect answers that were generated by some KA10 instructions when presented with corner-case operands (usually 4000000000000).

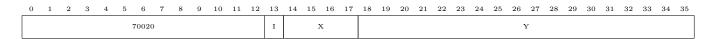

Non-I/O instructions use the standard PDP-10 instruction format.

| 0 1 2 3 4 5 6 7 8 | 9 10 11 12 13 14 15 16 17 | 18  19  20  21  22  23  24  25  26  27  28  29  30  31  32 | 33 34 35 |

|-------------------|---------------------------|------------------------------------------------------------|----------|

| F                 | A I X                     | Y                                                          |          |

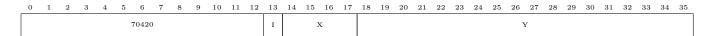

I/O instructions have bits [00..02] = 111, and use the old-style I/O instruction format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   | 7 |   |   |   |   | D |   |   |   |    | С  |    | I  |    | 2  | X  |    |    |    |    |    |    |    |    |    | 3  | Y  |    |    |    |    |    |    |    |    |

The D field specifies the device and the C field specifies the I/O command in the traditional way. The APR does not implement BLKI (C = 0) or BLKO (C = 2), and the behavior of an instruction with a C field of 0 or 2 is undefined (the implementation treats BLKI as DATAI and treats BLKO as DATAO). By convention, bits D[03..05] specifies the major device, and bits D[06..09] specifies the register within the device, if needed.

ITS was originally designed for the KA10 (and its predecessor, the 166), and although ITS can (and was) made to work on newer models of the PDP-10, the executive mode architecture of those newer models (process tables, page failures that are not reported via a PI) is somewhat at odds with the design. For this reason the executive mode architecture of the APR resembles that if the KA10, albeit one with paged memory management; there is a single block of ACs, the MUUO and PI vectors are in fixed locations in low memory, and traps and errors are reported

using the PI system.

The APR blocks internal I/O devices (APR, PI) are considerably different from that of the KA10; the set of traps and errors is different, any trap or error can be assigned to one of two PI levels, and there are some special features to simplify the ITS context switch.

#### 2.2 Flags and PC

| O           | 1           | 2           | 3           | 4           | 5      | 6 | 7 | 8 | 9 | 10 | 11          | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|-------------|-------------|-------------|-------------|-------------|--------|---|---|---|---|----|-------------|----|----|----|----|----|----|----|----|----|---------|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

| A<br>O<br>V | C<br>Y<br>0 | C<br>Y<br>1 | F<br>O<br>V | F<br>P<br>D | C<br>M |   |   | 0 |   |    | F<br>X<br>U | C  |    |    | 0  |    |    |    |    |    |         |    |    |         |    | Р  | С  |    |    |    |    |    |    |    |    |

The APR has no public mode, so bit [00] is always the AOV flag, and bit [07] is always 0. The APR has no user I/O mode nor previous mode, so bit [06] is always 0. The APR has no address failure inhibit, so bit [08] is always 0. The APR has a KA10-like APR trap architecture, so bits [09..10] (the TRAP1 and TRAP2 flags) are always 0.

The FPD flag is used by ILDB and IDPB to distinguish between the case where the byte pointer needs to be incremented before the byte is loaded or deposited (FPD = 0), and the case where the increment is not needed because it has already happened (FPD = 1), because the ILDB and IDPB instructions can be interrupted after the byte pointer has been incremented (BLKI and BLKO would have a similar problem if they were implemented, but they are not). ILDB and IDPB set FPD = 1 if they are interrupted after the byte pointer has been incremented, and set FPD = 0 if they run to completion. A few other instructions (IBP, PUSHJ, JSR, JSP) also set FPD = 0 if they run to completion (the fake JSR that is part of a PI sequence sets FPD to 0 just like a real JSR).

A user mode program (CM = 1) can only set CM to 0 by taking an interrupt or executing an MUUO.

#### 2.3 JRST

The APR, like the KA10, treats the AC field of JRST as a set of bits, each of which enables a special function.

- [09] If one or more priority interrupt levels are active dismiss the highest priority level; do nothing if no priority interrupt levels are active

- [10] Halt.

- [11] Restore the flags from the left half of the word last read by the effective address calculation, be it an indirect address word or an accumulator used as an index register. If the effective address calculation does not read any words (if the initial instruction word does not specify indirection or indexing) the flags are restored from the left half of the instruction word. A JRST with bit [11] set to 1 only loads CM if CM is set to 0; a program running in user mode, with CM set to 1, cannot set CM to 0.

- [12] Set CM to 1 (user mode).

In executive mode (CM = 0) all special functions are allowed, although bit [12] is ignored if both bit [11] and bit [12] are set to 1.

In user mode (CM = 1) only the special function enabled by bit [11] is allowed. A JRST with any or all of bits [09], [10], or [12] set to 1 is treated as an MUUO.

The APR implements JRST with bit [11] set to 1 by keeping track of the left half of the last word as a side effect of the evaluation of the effective address. Some implementations (for example, the KS10), re-evaluated the effective address assuming that PC-1 was the address of the JRST, which is incorrect in some cases (for example, when the JRST is the target of an XCT).

#### 2.4 MUUO and LUUO

The APR handles LUUO and MUUO instructions in almost the same way. A word containing the LUUO/MUUO opcode in bits [00..08], the LUUO/MUUO accumulator field in bits [09..12], zeros in bits [13..17], and the effective address in bits [18..35] is stored in some location 000040, and then the instruction in some location 000041 is executed.

If the instruction is an MUUO then the instruction word is stored in location 000040 of the executive mode address space, and the instruction in location 000041 of the executive mode address space is read and executed in (temporarily forced) executive mode; if the instruction in location 000041 is a JSR to the MUUO handler it will store FL,,PC+1 in the usual way and the return address will be that of the instruction immediately after the MUUO. If the instruction is a jump the APR will remain in executive mode; the CM flag will be set to 0 (JSR and JSP, as always, also set the FPD flag to 0).

If the instruction is an LUUO then the instruction word is stored in location 000040 of the current mode address space, and the instruction in location 000041 of the current mode address space is read and executed as an ordinary (non-interrupt) instruction in the current mode; if the instruction in location 000041 is a JSR to the LUUO handler it will store FL,,PC+1 in the usual way and the return address will be that of the instruction immediately after the LUUO.

Note that an LUUO and an MUUO end up being identical in executive mode, although their processing details are different.

If an MUUO is executed, and the instruction in location 000041 of the executive mode virtual address space contains an LUUO, the APR will execute the LUUO in (temporarily forced) executive mode, which will effectively make it an MUUO.

#### 2.5 XCTR and XCTRI

Executive mode software needs to be able to access system call parameters in the user mode address space. The APR makes this straightforward by allowing executive mode software to modify the behavior of the XCT instruction so that a variety of useful subsets of the memory references made by the executed instruction use the user mode

address space, even if the CM bit of the flags specifies executive mode.

| 0 | 1 | 2 | 3 | 4   | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|-----|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   | 256 |   |   |   |   |   | A  | A  |    | I  |    | 2  | ζ  |    |    |    |    |         |    |    |         |    | ,  | 7  |    |    |    |    |    |    |    |    |

The XCTR and XCTRI instructions execute the instruction in the memory location specified by the effective address, and use the A field to hold a code that specifies which of the memory references made by the executed instruction should reference the user mode address space.

Each memory reference made during the execution of an instruction belongs to one of five memory reference classes.

- IF Instruction fetches.

- E1 Index register references and memory references that are part of the effective address calculation of instructions, including the index register in the original instruction word.

- D1 Memory references that are simple memory operands, including the source operand of PUSH, the destination operand of POP, the destination operand of BLT, and the (first) byte pointer word.

- E2 Index register references and memory references that are part of the effective address calculation of byte pointers, including the index register reference in the (first) byte pointer word (this bit would also control source effective address calculations and operands in EXTEND, but the APR does not implement EXTEND.

- D2 Memory references that are byte data, and the source operand in BLT (this bit would also control destination effective address calculations and operands in EXTEND, but the APR does not implement EXTEND).

These are the same meanings of E1, D1, E2, and D2 that are used by the Tenex/TOPS-20 PXCT instruction, and inside the APR block itself.

Bits [10..12] of the A field encode several interesting selections of the E1, D1, E2, and D2 bits. The encoding is as follows.

| ITS Name      | A[1012] | IF | E1 | D1 | E2 | D2 |

|---------------|---------|----|----|----|----|----|

| -             | 0       | -  | -  | -  | -  | -  |

| XR,XW,XRW,XBW | 1       | -  | -  | Х  | -  | -  |

| XBR           | 2       | -  | -  | -  | -  | х  |

| XBRW          | 3       | -  | -  | Х  | -  | Х  |

| XEA           | 4       | -  | X  | -  | -  | -  |

| XBYTE         | 5       | -  | -  | Х  | Х  | Х  |

| -             | 6       | -  | -  | -  | -  | -  |

| -             | 7       | -  | -  | -  | -  | -  |

Bit [09] of the A field specifies how errors on I/O and relocated memory cycles should be reported. If this bit is 0 (XCTR) then errors are reported in the normal fashion; the current instruction is flushed, the HE or SE flag in the APR device is set, and a PI is generated if enabled. If this bit is 1 (XCTRI) then the current instruction is flushed and the PC is incremented by 2 so that the instruction after the current instruction is skipped. The status register in PAG is updated on soft errors in both cases; PI routines that use XCTRI will need to save and restore the status register in PAG to avoid confusion.

Note that the XCTR instruction encodes the A field in a way that is different from the encoding used by the A field of DEC-style PXCT. It exploits the fact that ITS uses only a subset of the legal PXCT A field values in order to find space in the A field for the bit that is used to distinguish between XCTR and XCTRI.

XCTRI skips on both hard and soft errors. XCTRI is normally used to read/write a location in user space from executive mode, with the skip telling the executive mode program that the read/write failed for some PAG-related reason. One might argue that XCTRI should only skip on soft errors, so that hard errors are not lost. On the other hand, if XCTRI skips on both hard and soft errors it can be used by the ROM program to avoid a double hard error halt should an E or D command be aimed at a non-existent location. The second design was selected, but its not quite the right thing.

I/O cycles are treated as relocated cycles to allow the console program to use XCTRI to avoid a double hard error halt if an E or D command is aimed at a device register that does not exist. Normal software might find this feature useful for things like testing for the existence of a device.

The XCTR instruction only performs its relocation function when executed in executive mode. The A field is ignored in user mode.

Relocated references to locations 0-17 normally access locations 0-17 of the user mode address space (the shadow locations, normally hidden by the accumulators), but the PAG block has the ability to redirect these references to a special AC block. ITS uses this feature to relocate references to these locations to one of the two AC blocks in the per-job variables (UUOACS, AC0S-AC17S).

The APR does not optimize the BLT case where the destination address is equal to the source address + 1 (the filling memory with a constant value case). It does not, therefore, need to do anything special to deal with the case where the BLT is the target of an XCTR or XCTRI and the code is XBR or XBW.

#### 2.6 Traps and Errors

The APR has six condition flags that capture various exceptional events.

The E1 and U1 flags capture trap-1 (arithmetic overflow) events. The E1 flag captures trap-1 events that happen in executive mode, and the U1 flag captures trap-1 events that happen in user mode.

The E2 and U2 flags capture trap-2 (push-down overflow) events. The E2 flag captures trap-2 events that happen in executive mode, and the U2 flag captures trap-2 events that happen in user mode.

The SE flag captures soft error events. The SE flag becomes set when the PAG block cannot successfully translate

a virtual address into a physical address (that is, if it gets a page failure).

The HE flag captures hard error events. The HE flag becomes set when the BIO block cannot map an I/O reference onto one of it's I/O devices (that is, if D[03..05] does not specify a legal I/O device). The HE flag also becomes set when the PAG block cannot successfully translate a virtual address into a physical address and the SE flag is already set (double soft error).

Software can arrange (by setting the appropriate bits in the APR device) that any of these six condition flags generate PI requests on one or both of two PI levels; having two levels allows conditions that correspond to fatal events to use a high-priority PI level and conditions that correspond to non-fatal events to use a low-priority PI level.

The APR guarantees that if an instruction sets a flag, the flag is configured to generate a PI, and the PI can be recognized, then the PI will be recognized before the next instruction begins execution. Traps and errors are reported using interrupts, but from a practical point of view, they can be treated as precise. The next instruction is not read and ignored (even though this would have simplified the implementation) so software does not need to handle the troublesome situation where an instruction gets a trap, the read of the next instruction (which is is ignored) gets another error, and both the trap and the (bogus) error get reported.

The trap flags (U1, U2, E1, E2) are set when the instruction that caused the trap completes, so if one of these flags causes a PI, the PC saved by the PI will point to the instruction after the instruction that set the trap flag. The error flags (HE, SE) are set when the instruction that caused the error is abandoned, so if one of these flags causes a PI, the PC saved by the PI will point to the instruction that set the error flag, and when the PI is dismissed the instruction that set the error flag will be re-executed.

The PI level assignments for trap and/or error handlers must be chosen so that the PI routines run at a higher priority than any code that might actually cause the events. At best, a trap will stick around until the JEN, when the trap PI handler will run, and promptly get very confused, since the saved PC has nothing to do with the PC at the time of the trap. At worst, an error will cause the APR re-execute the failing instruction, get another error, and get a double-error halt.

TOPS10 6.03 runs the APRs PI handler at high priority. There are comments in the code that say happens only if user is enabled when monitor causes condition and store offending PC so we can fix code, which suggests that user jobs that enabled trapping were rare enough that occasional the occasional trap in the monitor was not a big deal (this code is just after the label APRER0 in CLOCK1.MAC). TENEX 134 does essentially the same thing. ITS does the same sort of thing as well (look at the code after the labels AROV and/or ARFOV) but it runs the APR PI handler at low priority (CLKCHN = 7) so it seems that traps in PI handlers could confuse things.

### 2.7 Priority Interrupts

A priority interrupt (PI) request on a level can be generated by hardware (the request signal from an I/O device is true) or by software (the software request signal associated with the level is asserted). The APR recognizes a PI request on a level if a PI is not already in progress on the level or on any higher priority level, the PI system is enabled, and the PI level is enabled.

The KL10, and the KS10 with microcode revisions before revision 47, recognized a software interrupt on a level even if the level was not enabled. The APR requires that the level be enabled, making it compatible with the KC10, and with the KS10 with microcode revision of 47 or later. ITS is not sensitive to this difference, since the trouble it caused was resolved long ago, and requiring the level to be enabled is the more modern interpretation.

The APR checks for PI requests just before it begins reading an initial instruction word, just before it begins reading the target instruction word of an XCT, just before it begins writing the F/A/EA word into location 000040 on a UUO, and just before it begins reading any indirect addressing word (including any byte pointer word, which can be considered to be a kind of indirect addressing word). The APR also checks for PI requests just before it loops back to move an additional word on a BLT. These checks ensure that is possible for a PI to break out of a within-an-instruction loop.

If the APR finds one or more PI requests it picks the one having the highest priority, and begins recognizing that PI request. The APR recognizes a PI request on level N by setting the in-progress flag for level N, reading an instruction from executive mode location 000040+2\*N, and executing the instruction in (temporarily forced) executive mode.

The interrupt instruction is not really executed by the APR. The only instruction that is legal as an interrupt instruction is JSR (264000,,EA), and it is easier to execute the JSR using a dedicated logic sequence (all it needs to do is write FL,,PC into executive mode location EA, update FL in the manner of a JSR, and write EA+1 into PC).

Restricting the set of legal interrupt instructions to simplify their PI handling was commonplace in PDP-10 designs; the KS10, for example, only allowed JSR and XPCW as interrupt instructions.

If the APR begins recognizing a PI request, but cannot complete recognizing the PI request (because it cannot read the instruction from executive mode location 000040+2\*N, or the instruction is not of the form 264000,,EA, or it cannot write FL,,PC to executive mode location EA) the APR halts.

#### 2.8 Halts

The PDP-10 architecture allows a APR to halt; when halted a APR does not execute instructions until it is restarted by some explicit command, either from a switch on a front panel, or by a command executed by a front-end processor, depending on the implementation.

The PDP-10/X APR supports halt, but barely. When the APR halts it stops executing instructions, but there is no way to restart it other than resetting the entire system. This is acceptable because the APR is only halted in the most desperate of situations; in slightly less desperate situations control gets passed to EDDT, which supports the same kind of low-level debugging as a front panel, but with a nicer interface.

A normal halt happens when a HALT instruction is executed.

An abnormal halt happens when the APR gets into a state in which forward progress is impossible. Currently forward progress is considered to be impossible if a hard error is detected and the HE flag is set (double hard error), or if the APR begins but cannot complete a PI entry sequence (either because of a hard or soft error on any of the memory references associated with the PI entry sequence, or because the interrupt instruction is not a JSR instruction).

There is no way to force the APR to halt; such a switch would not be terribly useful. There is also no way to determne the address at which the APR has halted; it would be nice to be able to do so, but there is no obvious way to do it.

#### 2.9 Identification

Sometimes it is necessary for software to identify the implementation of the PDP-10 architecture upon which it is running. This is done with code sequences that deliberately touch corner-cases of each implementation, and identify the implementation by understanding *exactly* how each implementation behaves.

The usual code sequences identify the APR as a KI10; it does not have a PC-change flag (so it's not a PDP-6), a carry from the right half of an AOBJN does not effect the left half (so it's not a KA10 or a FOONLY), and the sequence MOVEI T,0 / BLT T,0 leaves 0 in T (the traditional hallmark of the KI10; the KL10 and the KS10 leave 1,,1 in T).

The APR and the KI10 can be distinguished by the fact that the APR has a 10-bit floating point exponent path, whereas the KI10 has a 9-bit path, and as such, mis-reports certain corner-cases of floating point exponent over-flow/underflow (the sequence MOVSI T,201400 / FSC T,377 results in a floating point overflow on the APR, but does not on the KI10, even though it should).

#### 2.10 CONI APR,E

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |       |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |         |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   | 70024 | 1 |   |   |    |    |    | I  |    | 2  |    |    |    |    |    |    |    |    |         |    | ,  | Y  |    |    |    |    |    |    |    |    |

| Į |   |   |   |   |   |   |       |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |         |    |    |    |    |    |    |    |    |    |    |    |

Read the status of the APR into location E. The word read has the following format.

|             |   |   |     |   |   | 7 |   |   |   |   |   |   |   |   | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 |   |   |   |   |   |    |    | 34 | 35 |

|-------------|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|---------|----|---|---|---|---|---|----|----|----|----|

| E           | E | E | E   | E | E | E | Т | Т | T | Т | T | Т |   | Т |    |    |    |    |    |    |         | F  | F | F | F | F | F | E  | Т  |    |    |

| E<br>H<br>E | S | E | E   | U | U | I | н | S | E | E | U | U |   | I |    |    |    |    |    |    |         | н  | S | E | E | U | U | E  | I  |    |    |

| E           | E | 2 | 1 1 | 2 | 1 | A | Е | E | 2 | 1 | 2 | 1 | l | Α | l  |    |    |    |    |    |         | E  | E | 2 | 1 | 2 | 1 | B. | R. |    |    |

- EHE Error interrupt enable for the hard error flag.

- ESE Error interrupt enable for the soft error flag.

- EE2 Error interrupt enable for the executive mode trap-2 flag.

- EE1 Error interrupt enable for the executive mode trap-1 flag.

- EU2 Error interrupt enable for the user mode trap-2 flag.

- EU1 Error interrupt enable for the user mode trap-1 flag.

- EIA The PI assignment for the error interrupt. If EIA is 0 the error interrupt is not connected to the PI system.

- THE Trap interrupt enable for the hard error flag.

- TSE Trap interrupt enable for the soft error flag.

- TE2 Trap interrupt enable for the executive mode trap-2 flag.

- TE1 Trap interrupt enable for the executive mode trap-1 flag.

- TU2 Trap interrupt enable for the user mode trap-2 flag.

- TU1 Trap interrupt enable for the user mode trap-1 flag.

- TIA The PI assignment for the trap interrupt. If EIA is 0 the trap interrupt is not connected to the PI system.

- FHE The hard error flag.

- FSE The soft error flag.

- FE2 The executive mode trap-2 flag.

- FE1 The executive mode trap-1 flag.

- FU2 The user mode trap-2 flag.

- FU1 The user mode trap-1 flag.

- EIR Indicates that an error interrupt is pending, even if the error interrupt is not connected to the PI system because EIA is 0.

- TIR Indicates that a trap interrupt is pending, even if the trap interrupt is not connected to the PI system because TIA is 0.

#### 2.11 CONO APR,E

Perform the function specified by the effective conditions E (an immediate quantity).

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 |   |   |   |    |        |   |     |   |   |   |   |   |   | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|---|---|---|----|--------|---|-----|---|---|---|---|---|---|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | S | R | С |    | -      | - | -   | M | M | M | M | M | M |    |    | -  |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | S | I | S | 5  | C<br>F | = | 느   | Н | S | E | E | U | U |    |    | 1  |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    | E | 0 | E | F. | F.     | E | .1. | E | E | 2 | 1 | 2 | 1 |    |    | A  |    |

- SSE Set the soft error flag.

- RIO Reset the I/O system. This does not effect anything associated with device 0, which means it does not reset anything in the APR or the PAG device.

- CSE Clear the soft error flag.

- SF Set the flags corresponding to the bits that are set in the mask (bits [25..30]).

- CF Clear the flags corresponding to the bits that are set in the mask (bits [25..30]).

- LE Load the error interrupt enables from the mask (bits [25..30]) and load the error interrupt PI assignment from the IA field (bits[33..35]).

- LT Load the trap interrupt enables from the mask (bits [25..30]) and load the trap interrupt PI assignment from the IA field (bits[33..35]).

- MHE Mask bit for hard error enables and/or flags.

- MSE Mask bit for soft error enables and/or flags.

- ME2 Mask bit for executive mode trap-2 enables and/or flags.

- ME1 Mask bit for executive mode trap-1 enables and/or flags.

- MU2 Mask bit for user mode trap-2 enables and/or flags.

- MU1 Mask bit for user mode trap-1 enables and/or flags.

- IA The value that can be loaded into the PI assignments for the error and/or trap interrupts.

The effect of a CONO APR that attempts to both set and clear a flag is undefined; the current design gives setting a flag priority over clearing a flag.

The SE bit is treated specially (that is, there is a SSE bit and a CSE bit) to allow a single CONO APR (the one in the context switch) to both load the trap enables for a job and set the SE flag should a high-priority PI routine wish to cause a fake soft error because an XCTRI detected an error.

#### 2.12 CONSZ APR,E

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | $^{25}$ | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|---------|----|----|----|----|----|----|----|----|----|----|

| Г |   |   |   |   |   |   |       |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |         |         |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   | 70030 | ) |   |   |    |    |    | I  |    | 2  |    |    |    |    |    |    |    |    |         |         | ,  | Y  |    |    |    |    |    |    |    |    |

| L |   |   |   |   |   |   |       |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |         |         |    |    |    |    |    |    |    |    |    |    |

Read the status of the APR (a word with the same format as described for CONI), mask it with the effective address E (an immediate quantity), and skip if the result is zero.

### 2.13 CONSO APR,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70034 | 1 |   |   |    |    |    | I  |    | 2  | x  |    |    |    |    |         |    |    |    |    | 7  | Y  |    |    |    |    |    |    |    |    |

Read the status of the APR (a word with the same format as described for CONI), mask it with the effective address E (an immediate quantity), and skip if the result is non-zero.

#### 2.14 CONI PI,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | $^{12}$ | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|---------|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70064 | 4 |   |   |    |    |         | I  |    | 2  | K  |    |    |    |    |         |    |    |    |    | 7  | Y. |    |    |    |    |    |    |    |    |

Read the status of the PI system into location E. The word read has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11     |   |   |   |   |        |   | 19 | 20 |   |   |   |   |   |   |   |   |   |              |   |   |   |   |        |

|---|---|---|---|---|---|---|---|---|---|----|--------|---|---|---|---|--------|---|----|----|---|---|---|---|---|---|---|---|---|--------------|---|---|---|---|--------|

|   |   |   |   |   |   |   |   |   |   |    | S      | S | S | S | S | S<br>R | S |    |    | I | I | I | I | I | I | I | _ | L | L            | L | L | L | L | E<br>7 |

|   |   |   |   |   |   |   |   |   |   |    | S<br>R | R | R | R | R | R      | R |    |    | P | P | P | P | P | P | P | G | E | $\mathbf{E}$ | E | E | E | E | E      |

|   |   |   |   |   |   |   |   |   |   |    | 1      | 2 | 3 | 4 | 5 | 6      | 7 |    |    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | E | 1 | 2            | 3 | 4 | 5 | 6 | 7      |

- SR1-7 Software request flags for levels 1-7.

- IP1-7 In-progress flags for levels 1-7. The in-progress flag for level n is set when an interrupt request is accepted on level n, and the highest priority (lowest n) in-progress flag is reset by JRST 10 or JRST 12.

- GE The global enable flag.

- LE1-7 Enable flags for levels 1-7.

At reset all of the software request flags, all of the in-progress flags, the global enable flag, and all of the enable flags are set to 0.

An SRn bit makes a request on a level even if the LEn bit for the level is clear; only GE needs to be set. This is compatible with the last models of the PDP-10 running the newest microcode, but is incompatible with the KA10, which required that the LEn bit be set. ITS always sets the LEn bits.

An SRn bit remains set until it is cleared by software. This is compatible with all models of the PDP-10 except the KA10, which cleared SRn upon delivery of a PI at level n. ITS conditionalizes the explicit clearing of SRn bits on a model-by-model basis.

### 2.15 CONO PI,E

Perform the function specified by the effective conditions E (an immediate quantity).

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 |             |             |             |             |             |        |             |        |        |        |        |        |        |        |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|-------------|-------------|-------------|-------------|-------------|--------|-------------|--------|--------|--------|--------|--------|--------|--------|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    | C<br>S<br>R | R<br>P<br>I | S<br>S<br>R | S<br>L<br>E | C<br>L<br>E | G<br>E | S<br>G<br>E | L<br>1 | L<br>2 | L<br>3 | L<br>4 | L<br>5 | L<br>6 | L<br>7 |

- CSR Clear the software request(s) corresponding to the bit(s) that are set in the mask (bits [29..35]).

- RPI Reset the PI system. All of the software request bits, all of the in-progress bits, the global enable bit, and all of the level enable bits are cleared.

SSR Set the software request(s) corresponding to the bit(s) that are set in the mask (bits [29..35]).

SLE Set the level enable bit(s) corresponding to the bit(s) that are set in the mask (bits [29..35]).

CLE Clear the level enable bit(s) corresponding to the bit(s) that are set in the mask (bits [29..35]).

CGE Clear the global enable.

SGE Set the global enable.

L1-7 Mask bits for levels 1-7.

The effect of a CONO PI that attemts to both set and clear a flag is undefined; the current design gives setting a flag priority over clearing a flag.

#### 2.16 CONSZ PI,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70070 | ) |   |   |    |    |    | I  |    | 2  | x  |    |    |    |    |    |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

Read the status of the PI system (a word with the same format as described in CONI PI), mask it with the effective address E (an immediate quantity), and skip if the result is zero.

#### 2.17 CONSO PI,E

| O | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   | 7 | 70074 | ı |   |   |    |    |    | I  |    | 2  | x  |    |    |    |    |    |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

Read the status of the PI system (a word with the same format as described in CONI PI), mask it with the effective address E (an immediate quantity), and skip if the result is non-zero.

## **PAG**

PAG is the pager and the memory controller. It responds to all memory references generated by APR, translating virtual memory addresses into physical memory addresses in a way that is appropriate for ITS, when necessary.

When paging is disabled programs can only reference some (usually the lowest) 256KW of the 4096KW physical address space. When paging is enabled programs can reference up to 256K words of virtual address space, consisting of up to 256 1K word virtual pages, each mapped to any of the 4096 1K word physical pages in the 4096K word physical address space.

The mapping between virtual pages and physical pages is stored in page tables located in physical memory. Each page table is 64 words long and contains mappings for 128 virtual pages. Page tables are aligned on 64-word boundaries in the physical address space; this causes no trouble for ITS (which stores page tables in the front of the user variable block, which is easily aligned, since on the KL10/KS10 it also served as the UPT, which had alignment requirements), and eliminates the need for an adder in a critical path.

There are four page tables; two page tables map the low and high 128K words of the executive mode virtual address space, and two page tables map the low and high 128K words of the user mode virtual address space. The four page tables are pointed to by four page table base registers.

The left half of each word in a page table contains the mapping for an even page (that is, a page with VA[10]=0) and the right half of each word in the page table contains the mapping for an odd page (that is, a page with VA[10]=1).

| 0 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|-----|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Р   |   |   | A |   |   |   |   |   |    | PF | N  |    |    |    |    |    | F  | •  |    |    | A  |    |    |    |    |    |    | PI | 'n |    |    |    |    |    |

The P field is the protection code. No access is allowed if the protection code is 0. Read access is allowed if the protection code is 1, 2, or 3, Write access is allowed if the protection code is 3. Read-only pages normally have protection code 1; protection code 2, usually called *read/write first*, is used to trap the first write to pages that would normally have protection code 3.

The A field is the age flag. It does not participate in translation or protection, but it is set to 0 when the page table entry is used by the PAG block to translate an address (when the pager sets the A bit to 0 is disturbs no other bits in the page table entry, including bits [02..03] and bit [05]).

The PPN field is the physical page number. The PPN field is 12 bits wide, so there can be 4096 physical pages, which is enough to address up to 4096KW of memory.

PAG contains two 256-entry RAMS which cache the most recently fetched page table entry for each of the virtual pages in each of the address spaces. The entry in the RAM corresponding to the virtual page is loaded any time a page table entry is fetched from a page table. When a virtual to physical translation is needed, PAG first looks in the RAM to see if it contains a page table entry that can satisfy the translation. If it does then the memory access proceeds. If it does not (either because the entry was not valid, or because the protection check failed) the page table lookup process begins.

Software can invalidate individual entries and/or all 256 entries in either or both of the page table entry cache RAMS using the DATAO PAG+1 instruction. In addition, any time a page table base register is updated using a DATAO PAG+4, DATAO PAG+5, DATAO PAG+6, or DATAO PAG+7 instruction all 256 entries in the RAM associated with the virtual address space mapped by the updated page table base are invalidated.

Note that because the page table lookup process is begun anytime the page table entry cache cannot satisfy the request, it is not necessary to invalidate an entry in the page table entry cache if a page table entry is changed from invalid to valid, or from a state which does not allow writing into a state that does allow writing. It is only necessary to invalidate an entry in the page table entry cache when a page table entry is switches to a more restrictive protection code.

Bulk invalidations of the page table entry cache are performed in a way that minimizes the impact of doing so. When a page table entry cache RAM needs to be bulk invalidated, it is placed into the invalidating state. In this state the cache is invalidating one entry per cycle, so the whole RAM is invalidated in 256 cycles. If software makes a request that requires the use of the RAM while it is invalidating the request is processed via a full page table lookup, and the page table entry is not written into the RAM. Instructions continue to be executed during the invalidation, but memory operates at about half speed. Note also that accesses made to the executive mode address space are not stalled while the user mode page table entry cache RAM is invalidating, so when the operating system switches jobs, some of the invalidation time is overlapped with the executive mode code that is restoring the state of the job.

APR does not check write access for the memory operand of an instruction that both reads and writes memory until the write actually happens; a DIVM whose memory operand is 0 and in a location that cannot be written will get a no divide trap rather than an error from PAG on the failed write.

When PAG detects that a cycle generated by the currently executing instruction cannot be completed it captures some information about the cycle in a register within PAG, and completes the read or write with a soft error. The APR abandons the currently executing instruction without updating any state (so the PC is left pointing at the instruction that could not be completed). The soft error acknowledge normally sets the SE flag and generates a PI. If a PI is not generated the instruction is re-executed, which may result in a double soft error (which normally sets the HE flag and generates a PI) or a double hard error (which generates a halt).

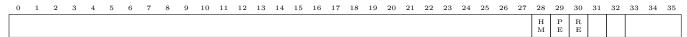

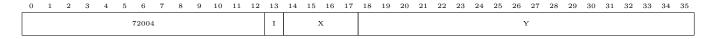

#### 3.1 CONI PAG+0,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70424 | 1 |   |   |    |    |    | I  |    | 2  | x  |    |    |    |    |         |    |    |    |    | 7  | Y  |    |    |    |    |    |    |    |    |

Read the status of PAG into location E. The word read has the following format.

| 0 1 | . 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28     | 29     | 30     | 31 | 32 | 33 | 34 | 35 |

|-----|-----|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|--------|--------|----|----|----|----|----|

|     |     |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | H<br>M | P<br>E | R<br>E |    |    |    |    |    |

- HM Highest moby. Determines which 256KW region of the physical address space referenced by reads/writes when the PE bit is 0. If the HM bit is 1 then the highest 256KW is referenced. If the HM bit is 0 then the lowest 256KW is referenced.

- PE Paging enable. If the PE bit is 1 reads/writes reference (up to) 256KW of virtual address space directed to (up to) 256 1KW pages located anywhere in the 4096KW (512KW) physical address space. If the PE bit is 0 reads/writes reference 256KW of virtual address space redirected to the 256KW of the physical address space specified by the HM bit.

- RE ROM enable. If the RE bit is 1 reads from virtual locations 400000-777777 reference 128 copies of the 1KW ROM, and writes to virtual locations 400000-777777 are ignored. If the RE bit is 0 virtual locations 400000-777777 receive no special treatment.

The normal paging off configuration has HM = 0, PE = 0, and RE = 0. The normal paging on configuration has PE = 1, and RE = 0. The console and bootstrapping ROM has HM = 1, PE = 0, and RE = 1/0.

Power-up reset sets HM to 1, PE to 0, and RE to 1. A software-generated I/O reset (caused by CONO APR, 200000) does not effect HM, PE, or RE.

The layout of the bits in this register anticipates adding a PAG interrupt at some point in the future; bit [31] would be the IE flag, bit [32] would be the IR flag, and bits [33..35] would be the PI level assignment.

#### 3.2 CONO PAG+0,E

Set up the PAG device from the effective conditions E as shown.

HM Highest moby.

PE Paging enable.

RE ROM enable.

The layout of the bits in this register anticipates adding a PAG interrupt at some point in the future; bit [31] would be the IE flag, bit [32] would be unused, and bits [33..35] would be the PI level assignment.

#### 3.3 CONSZ PAG+0,E

| 0 1 2 3 4 5 6 7 | 8 9 10 11 12 | 13 | 14 1 | 5 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|-----------------|--------------|----|------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 70430           |              | I  |      | x    |    |    |    |    |    |    |    |    |    | ,  | Y  |    |    |    |    |    |    |    |    |

Read the status of PAG (a word with the same format as described in CONI PAG), mask it with the effective address E (an immediate quantity), and skip if the result is zero.

#### 3.4 CONSO PAG+0,E

Read the status of PAG (a word with the same format as described in CONI PAG), mask it with the effective address E (an immediate quantity), and skip if the result is non-zero.

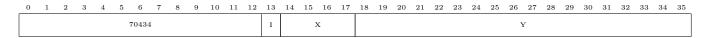

### 3.5 DATAI/DATAO PAG+0,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | $^{12}$ | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|----|---|---|----|----|---------|----|----|----|----|----|----|----|----|---------|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70404 | Į. |   |   |    |    |         | I  |    | 2  | ĸ  |    |    |    |    |         |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12      | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21      | 22 | 23 | 24      | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   | 70414 | ı  |   |   |    |    |         | I  |    | 2  | ζ. |    |    |    |    |         |    |    |         |    |    | Y  |    |    |    |    |    |    |    |    |

Read/write the register that describes the most recent soft error encountered by PAG. The register has the following format.

| 0      | 1      | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27     | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|--------|--------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|--------|----|----|----|----|----|----|----|----|

| W<br>R | U<br>M | 1 | P |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |         |    | 1  | V<br>A |    |    |    |    |    |    |    |    |

WR Set to 1 if the error happened on a write, and set to 0 if the error happened on a read.

- UM Set to 1 if the error happened on a user mode read/write, and set to 0 if the error happened on an executive mode read/write. Executive mode programs can generate traps with UM = 1 with XCTR or XCTRI.

- P The P field of the page table entry that was accessed and determined that the read/write should complete with a soft error.

- VA The virtual address of the read/write that generated the error.

Bits [06..17] are unused, so there are enough bits for a full 30-bit VA in some future extended addressing design, even though it is unlikely that any such design would be done, since ITS does not understand extended addressing.

This register is updated on any error generated by PAG, even errors that are generated by an instruction under an XCTRI that causes the APR to skip instead of generating APR PI (it needs to work this way to allow the code at label INTPFL to be written).

This register is read/write to allow a high-priority PI routine that uses XCTRI instructions to save and restore this register, since ITS processes page failures in a low-priority interrupt handler (APRCHN = 7). This is actually how ITS works when using a Systems Concepts paging box, but it is not obvious that this is the case (the save and restore is a side effect of SPM and LPMR instructions executed by the PI routine).

Power-up reset sets UM to 0, WR to 0, P to 0, and VA to 0. A software-generated I/O reset (caused by CONO APR, 200000) does not effect UM, WR, P, or VA.

#### 3.6 DATAO PAG+1,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | $^{12}$ | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | $^{25}$ | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|---------|---------|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70454 | ı |   |   |    |    |         | I  |    | 2  | x  |    |    |    |    |    |    |    |         |         | -  | Y  |    |    |    |    |    |    |    |    |

Invalidate entries in PAGs page table entry cache specified by the contents of location E. The word read from location E has the following format.

|        |   | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|--------|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| E      | U | - |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | r  |    |    |    |    |    |    |    |    |

| l I    | I | 1 |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| I<br>E | E | S |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | 4  |    |    |    |    |    |    |    |    |

- EIE Set to 1 to enable invalidation of the executive mode virtual address space.

- UIE Set to 1 to enable invalidation of the user mode virtual address space.

- IS Set to 1 if this is an invalidate single (only the page table entry cache location that maps the virtual address specified by the IA field) and set to 0 if this is an invalidate all (all page table entry cache locations).

- IA The address being invalidated if the IS field is set to 1.

The ITS CLRPGM macro (flush the entire page table entry cache) can be implemented with DATAO PAG+1,[600000,,000000].

The standard CLRPT E instruction (flush the single page table entry cache location associated with address E in both address spaces) can be implemented with DATAO PAG+1,[700000,,E].

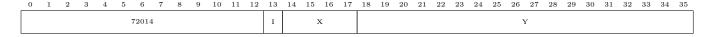

#### 3.7 DATAI/DATAO PAG+2,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70504 | ŀ |   |   |    |    |    | I  |    | 2  | ζ  |    |    |    |    |    |    |    |         |    |    | Y  |    |    |    |    |    |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24      | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   | 70514 | Ŀ |   |   |    |    |    | I  |    | 2  | ζ  |    |    |    |    |    |    |    |         |    |    | Y  |    |    |    |    |    |    |    |    |

Read/write the AC-block enable and the AC-block base register (the base register that ITS doesnt ever really name, but which the Systems Concepts ITS pager stored in word 7 of the 8-word LPMR/SPM block). The word has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23       | $^{24}$ | $^{25}$ | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----------|---------|---------|----|----|----|----|----|----|----|----|----|----|

| A |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | -  | A.<br>B. |         |         |    |    |    |    |    |    |    |    |    |    |

- AE The AC-block enable. If the AE bit is 1 reads/writes to virtual locations 0-17 are mapped to the 16-word block in physical memory whose address is specified by the AB field. If the AE bit is 0 reads/writes to virtual locations 0-17 are mapped in the standard way. Reads/writes to virtual locations 0-17 can only be generated using XCTR and XCTRI.

- AB The AC-block base. Set to bits [14..31] of the physical address of the 16-word AC block in memory. Bits [32..35] are unused, which means the 16-word AC block in memory must be aligned on a 16-word boundary.

The 16-word alignment restriction saves an adder in the critical path to getting a physical address to the memory, and causes no trouble, since the only values ITS ever puts in this register are fixed offsets from the start of the job variables (UUOACS and ACOS), and it's easy to align the job variables.

Power-up reset sets AE to 0 and AB to 0. A software-generated I/O reset (caused by CONO APR, 200000) does not effect AE or AB.

#### 3.8 DATAI/DATAO PAG+3,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|----|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70544 | Į. |   |   |    |    |    | I  |    | 2  | C  |    |    |    |    |    |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24      | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   | 70554 |    |   |   |    |    |    | I  |    | 2  | ζ. |    |    |    |    |    |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

Read/write the quantum timer, which is an 18-bit timer that increments every 4 microseconds (that is, by the 16 MHz system clock divided by 64) any time the APR is running at level 0 (that is, no PI is active). Nothing special happens when the quantum timer overflows (the quantum timer in the Systems Concepts ITS paging box for the KA10 generated an interrupt for this condition, but ITS did not use it, and actually went to considerable trouble to ensure that the interrupt did not happen).

The quantum timer in the Systems Concepts paging box was 19 bits wide and incremented at 1 MHz, but this size/rate was never really used; any time the value in the quantum timer was read it was immediately shifted right by 2 bits. The quantum timer in PAG increments at the desired rate, and as a side effect of doing so, is actually 1 bit wider than the one in the Systems Concepts paging box.

The word written/read has the following format.

| 0 | 1 | L | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Г  |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | ΛI |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 1  | 3  |    |    |    |    |    |    |    |    |

Power-up reset sets TMR to 0. A software-generated I/O reset (caused by CONO APR, 200000) does not effect TMR.

The simulator does not increment the quantum timer by 1 every 4 microseconds, but by 2500 every 10 milliseconds.

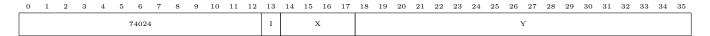

#### 3.9 DATAI/DATAO PAG+4,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|----|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70604 | Į. |   |   |    |    |    | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    | -  | Y  |    |    |    |    |    |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   | 70614 | ŀ  |   |   |    |    |    | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    |    | Y  |    |    |    |    |    |    |    |    |

Read/write the executive mode low segment base register (the base register ITS normally calls DBR4). The word written/read has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | E  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | L  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 1  | В  |    |    |    |    |    |    |    |    |    |    |    |    |    |

Note that bits [30..35] are unused, which means the 64-word page table must be 64-word aligned.

The 64-word alignment restriction saves an adder in the critical path to getting a physical address to the memory, and causes no trouble, since the only value ITS ever puts in this register is a constant.

All 256 entries in the executive mode page table entry cache are invalidated any time the executive mode low segment base register is written.

Power-up reset sets ELB to 0. A software-generated I/O reset (CONO APR, 200000) does not effect ELB.

#### 3.10 DATAI/DATAO PAG+5,E

| ( | ) | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | $^{12}$ | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|-------|----|---|---|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   | 70644 | Į. |   |   |    |    |         | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    | -  | Y  |    |    |    |    |    |    |    |    |

| ( | ) | 1 | 2 | 3 | 4 | 5 | 6     | 7  | 8 | 9 | 10 | 11 | 12      | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   |   | 70654 | ŀ  |   |   |    |    |         | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    | -  | Y  |    |    |    |    |    |    |    |    |

Read/write the executive mode high segment base register (the base register ITS normally calls DBR3). The word written/read has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | E  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    | ]  | H  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 1  | В  |    |    |    |    |    |    |    |    |    |    |    |    |    |

Note that bits [30..35] are unused, which means the 64-word page table must be 64-word aligned.

The 64-word alignment restriction saves an adder in the critical path to getting a physical address to the memory, and causes no trouble, since the only value ITS ever puts in this register is a constant.

All 256 entries in the executive mode page table entry cache are invalidated any time the executive mode high segment base register is written.

Power-up reset sets EHB to 0. A software-generated I/O reset (CONO APR, 200000) does not effect EHB.

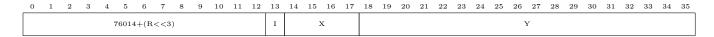

#### 3.11 DATAI/DATAO PAG+6,E

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | $^{21}$ | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   | 70704 | Ŀ |   |   |    |    |    | I  |    | 3  | ĸ  |    |    |    |    |         |    |    |         |    | -  | Y  |    |    |    |    |    |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21      | 22 | 23 | 24      | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   | 70714 | L |   |   |    |    |    | I  |    | 3  | ×. |    |    |    |    |         |    |    |         |    |    | Y  |    |    |    |    |    |    |    |    |

Read/write the user mode low segment base register (the base register ITS normally calls DBR1). The word written/read has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    | 1  | U  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | L  |    |    |    |    |    |    |    |    |    |    |    |    |    |

|   |   |   |   |   |   |   |   |   |   |    |    |    |    | l  |    |    |    |    |    |    | 1  | В  |    |    |    |    |    |    |    |    |    |    |    |    |    |

Note that bits [30..35] are unused, which means the 64-word page table must be 64-word aligned.

The 64-word alignment restriction saves an adder in the critical path to getting a physical address to the memory, and causes no trouble, since the only value ITS ever puts in this register is a fixed offset from the start of a job's variables (UPGCP), and it's easy to align the start of a job's variables (since the job's variables contain a UPT on some machines, and on some of these machines, the UPT needs to be aligned).

All 256 entries in the user mode page table entry cache are invalidated any time the user mode low segment base register is written.

Power-up reset sets ULB to 0. A software-generated I/O reset (CONO APR, 200000) does not effect ULB.

#### 3.12 DATAI/DATAO PAG+7,E

| C | ) | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|-------|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |   |   |   |   |   |   | 70744 | ı |   |   |    |    |    | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    | -  | Y  |    |    |    |    |    |    |    |    |

| 0 | ) | 1 | 2 | 3 | 4 | 5 | 6     | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|   |   |   |   |   |   |   | 70754 | Į |   |   |    |    |    | I  |    | 3  | ĸ  |    |    |    |    |    |    |    |    |    | -  | Y  |    |    |    |    |    |    |    |    |

Read/write the user mode high segment base register (the base register ITS normally calls DBR2). The word written/read has the following format.

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | $^{12}$ | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | $^{24}$ | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 |

|---|---|---|---|---|---|---|---|---|---|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|---------|----|----|----|----|----|----|----|----|----|----|----|